# Department of Computer Science 2nd Year Bachelor's Degree Computer Architecture

## Solution of Tutorial Series N°1

#### Exercise 1 :

| а  | b | С | d  | е | f | g | h | i | j | k |   | m  | n  |

|----|---|---|----|---|---|---|---|---|---|---|---|----|----|

| 11 | 3 | 5 | 10 | 9 | 7 | 1 | 2 | 6 | 4 | 8 | 9 | 13 | 14 |

**Exercise 2 :** Find the word or phrase that best matches the following descriptions:

**a)** Program that manages the resources of a computer for the benefit of the programs that run on that machine. **Operating System**

b) Program that translates from a high-level notation to assembly language. Compiler

c) Component of the processor that tells what to do according to the instructions. Control Unit

d) Interface that the hardware provides to the software. Instruction Set Architecture

e) Computer inside another device used for running one predetermined application or collection of software. Embedded System

#### Exercise 3:

- 1. Explain the main differences between high-level languages, assembly language, and machine language:

- **High-Level Language:** Uses instructions close to human language, hardware-independent. For example: C, Python.

- **Assembly Language:** Uses instructions closer to the hardware, a more human-readable representation of machine instructions.

- **Machine Language:** A sequence of bits interpreted directly by the processor, very difficult for a human to read.

- 2. Name the main components of a computer and describe their role in data processing:

- **Central Processing Unit (CPU):** Processes program instructions.

- **Memory (RAM):** Temporarily stores data and instructions used by the CPU.

- Input/Output Devices: Allow communication with the computer (keyboard, mouse, screen).

- Hard Drive/SSD: Permanently stores data.

- 3. Explain the role of the bus in communication between these components:

- The **bus** is a communication system that transfers data between internal components, such as memory, the processor, and input/output devices. It can be divided into the data bus (transfers data), the address bus (transfers memory addresses), and the control bus (manages control signals).

- 4. Identify and explain two major improvements in computer technology over the past few decades:

## Technological improvements:

- **Moore's Law:** Doubling the number of transistors in a processor approximately every two years, thereby increasing processing power.

- **Multicore Processors:** The integration of multiple cores within a single processor allows for parallel execution of tasks, improving overall system performance.

- 5. How do these improvements affect the performance of programs written in assembly language? Impact on assembly language:

- Programs written in assembly can directly benefit from hardware architecture improvements (such as pipelining and parallel execution), which allows for further optimization of register management, instructions, and calculations for increased performance.

- 6. What is the width of a processor that has 64 bits for data buses and 32 bits for its internal registers?

- It is a **32-bit processor**.

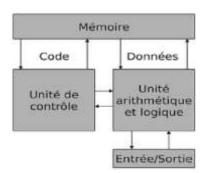

- 7. Complete the following Von Neumann machine diagram? (fill in the blank boxes)

## 8. Von Neumann Architecture vs. Harvard Architecture

The Von Neumann architecture is similar to the Harvard architecture, with the key difference being that it uses a single bus for both fetching instructions and transferring data. Therefore, operations must be scheduled accordingly. The Harvard architecture, on the other hand, uses two separate memory addresses for data and instructions, which allows simultaneous feeding of data on both buses. However, the more complex architecture increases the development cost of the control unit compared to the lower development cost of the simpler Von Neumann architecture, which uses a single unified cache.

## Exercise 4:

- Time of one rotation = 1 min / 7200 rotations = 60000 ms / 7200 Time of one rotation = 8.33 ms

- Time to access a block of 32 consecutive sectors = 8 ms (average seek) + 8.33 ms / 2 (average rotation latency) + 32/200 \* 8.33 (transfer time) = 8 + 4.17 + 1.33 = 13.5 ms

#### Exercise 5: Personal work to be done at home