Université 8 mai 1945 de Guelma Faculté de Mathématiques, D'Informatique et de Sciences de la Matière Département : Informatique

# Série N°2

## Exercice N°1

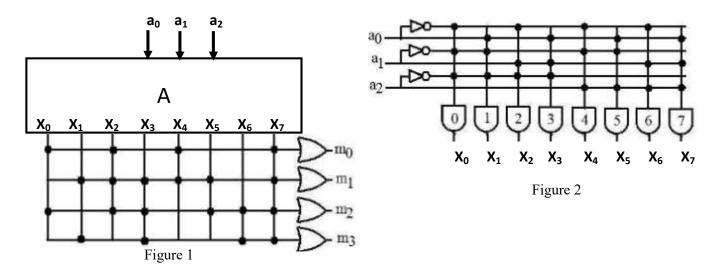

On considère le circuit de la figure 1 qui représente une ROM (*Read Only Memory*) déjà programmée, avec trois entrées (a<sub>2</sub> a<sub>1</sub> a<sub>0</sub>) et quatre sorties (m<sub>3</sub> m<sub>2</sub> m<sub>1</sub> m<sub>0</sub>).

- 1. A quoi correspondent les entrées et les sorties de cette mémoire ?

- 2. Que représente le circuit A ? et quel est son rôle ?

- 3. La figure 2 illustre le contenu du circuit A. Dresser la table de vérité de ce circuit puis en déduire les expressions des sorties (X<sub>0</sub> ..... X<sub>7</sub>) du circuit A en fonction des entrées (a<sub>2</sub> a<sub>1</sub> a<sub>0</sub>).

- 4. Donner les expressions des sorties (m<sub>3</sub> m<sub>2</sub> m<sub>1</sub> m<sub>0</sub>) en fonction des entrées (a<sub>2</sub> a<sub>1</sub> a<sub>0</sub>) de la ROM.

- 5. Donner un schéma représentatif simplifié de la ROM.

- 6. En déduire la capacité de cette mémoire.

## Exercice N°2

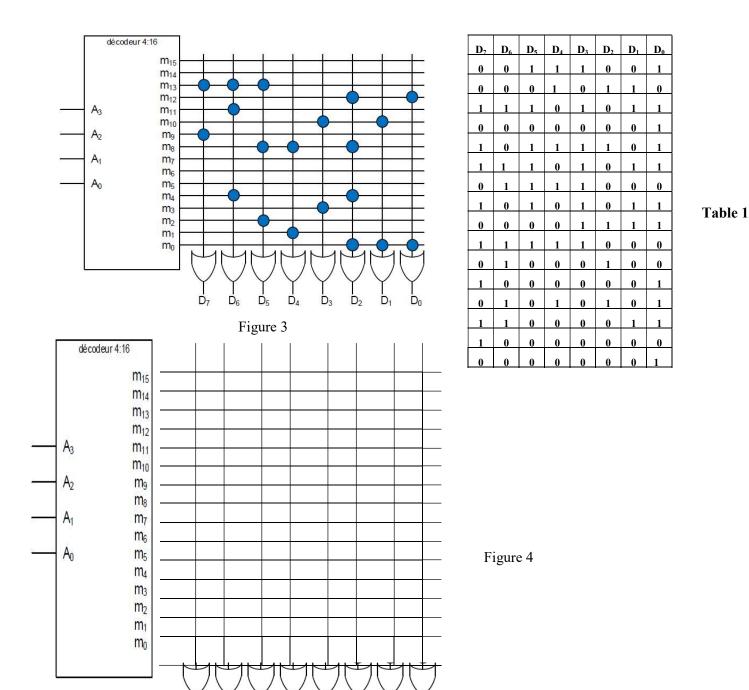

Soit le circuit fonctionnel d'une mémoire EPROM de la figure 3.

- 1. Donner les expressions de sortie du Décodeur 4:16 de la mémoire (sans dressement de la table de vérité).

- 2. Donner les expressions de sortie de la EPROM en fonction des sorties du décodeur.

- 3. Dresser la table binaire représentant le contenu de la EPROM.

- 4. Reprogrammer la mémoire selon la table 1 sur la figure 4 :

## Exercice N°3

Nous voulons concevoir une mémoire principale (MP) 2048 Ki mots de 2 octets à partir de circuits mémoire ayant un RAM de 21 bits et un RIM de 4 bits.

- 1. Quelle est la taille du bus de données et d'adresse de la MP.

- 2. Calculer la capacité de la MP en Mio.

- 3. Calculer la capacité des circuits mémoire en Mio.

- 4. Calculer le nombre de circuit nécessaire à la réalisation de la MP en spécifiant l'extension ligne et l'extension colonne?

- 5. Dresser le logigramme de la MP.

- 6. Quelles sont les puces mémoires actives lors de la lecture de l'adresse 0x0FFFFF

#### Exercice N°4

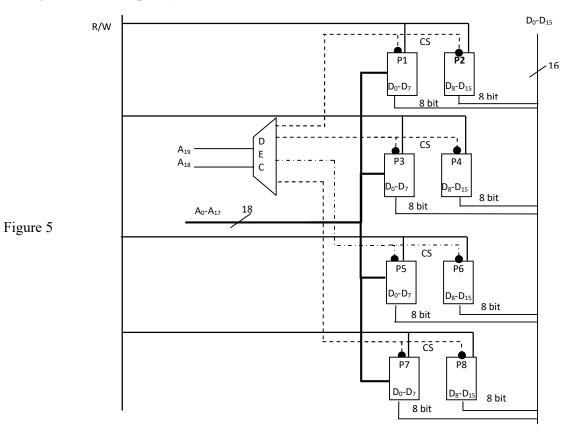

Soit le câblage de la mémoire principale de la figure 5

- 1. Calculé pour les puces :

- a. La largeur des mots.

- b. Le nombre de mots par puce.

- c. La capacité en Kio.

- 2. Calculer pour la mémoire principale :

- a. La largeur des mots.

- b. Le nombre de mots.

- c. La capacité en Mio.

- d. Exprimer la capacité calculée en (c) en mots de 8 bits et en mot de 4 bits.

- 3. Combien de puces mémoire il faut rajouter pour avoir une MP de 4 Mio.

- 4. Quelles sont les puces mémoires actives lors de la lecture des adresses : 0x3CAF0 et 0xCCAF0. (justifiez votre réponse)

#### Exercice N°5

Un processeur 64 bits stocke les données binaires qu'il traite dans des circuits intégrés de mémoire RAM. La capacité de chaque circuit mémoire est de 4 Mo, les données binaires étant organisées en mots de 64 bits. La capacité totale de l'ensemble des mémoires vives est de 32 Mo.

- 1. De combien de circuits différents est constitué l'ensemble de la mémoire vive associée à ce processeur ?

- 2. Donner le nombre de cases mémoires disponibles dans chaque circuit RAM ainsi que le nombre total de cases mémoires pour l'ensemble des circuits.

3. Quelle doit être la taille minimum du bus d'adresse de ce processeur ? Quelle est l'adresse la plus haute et l'adresse la plus basse (en hexadécimal) accessible par le processeur?

La taille du bus d'adresse sera désormais la taille minimum que vous venez de trouvez.

- 4. Parmi l'ensemble des bits constituant le bus adresse, donner le nombre de bits réservés à la sélection d'un circuit mémoire (boitier) et le nombre de bits réservés à la sélection d'un emplacement dans cette mémoire.

- 5. Donner les adresses de début et de fin des quatre premiers circuits en complétant le tableau cidessous.

| Circuit | $A_{21} A_{20}$ | A <sub>19</sub> | A <sub>16</sub> | A <sub>15</sub> | A <sub>12</sub> | A <sub>11</sub> | $A_8$ | $A_7$ | $A_4$ | $A_3$ | $A_0$ | Adresse Hexadécimale |  |

|---------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------|-------|-------|-------|-------|----------------------|--|

| RAM 3   |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Fin                  |  |

|         |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Début                |  |

| RAM 2   |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Fin                  |  |

|         |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Début                |  |

| RAM 1   |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Fin                  |  |

|         |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Début                |  |

| RAM 0   |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Fin                  |  |

|         |                 |                 |                 |                 |                 |                 |       |       |       |       |       | Début                |  |