## 1. Introduction

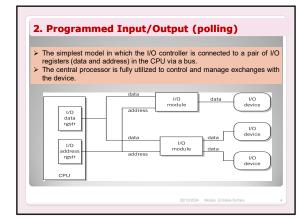

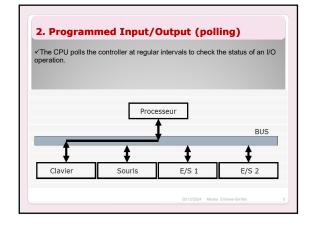

- It is the CPU that initiates all input or output operations.

- How can input/output operations be managed without degrading the performance of the entire machine?

- Three main methods of managing input/output operations are distinguished:

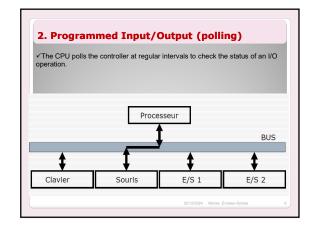

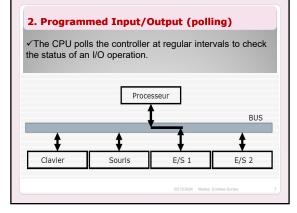

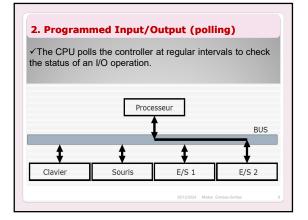

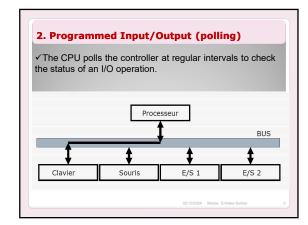

- 1. Programmed Input/Output (Polling).

- 2. Direct Connection with Interrupt.

- 3. Direct Memory Access (DMA).

1

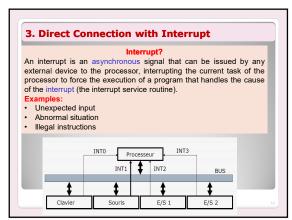

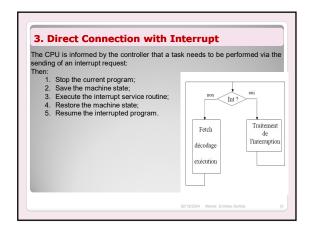

#### 3. Direct Connection with Interrupt

- The device uses the interrupt mechanism to signal that it is ready.

- All devices signal an event to the processor via a single interrupt line by setting the corresponding signal.

- To handle interrupts, the operating system has a set of interrupt management programs.

- When an interrupt is received, the currently running program is stopped in favor of the interrupt service routine.

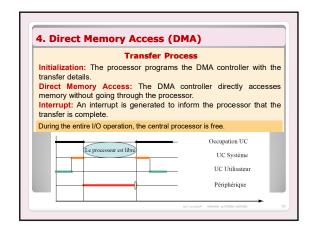

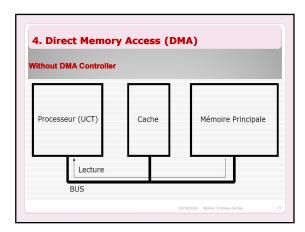

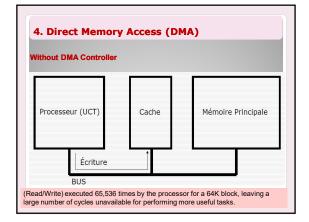

### 4. Direct Memory Access (DMA)

#### Problem?

The interrupt mechanism is very efficient, but the time used by the processor for the interrupt service routine and the driver should not be too significant.

#### Solutions:

> Decrease the number of interrupts.

Load data from main memory without using the central processor, using Direct Memory Access (DMA).

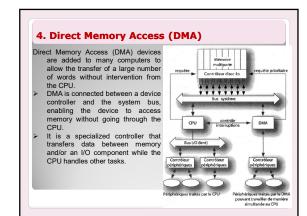

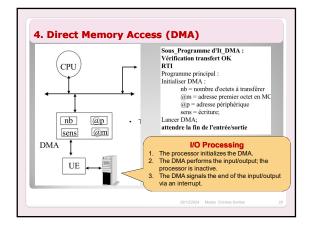

## 4. Direct Memory Access (DMA)

#### **Constitution of DMA**

- The hardware components include:

- > An address register

- > A count register

- > A control register (read or write)

- A buffer area for storing data

- > An active component, processor-like

#### 4. Direct Memory Access (DMA)

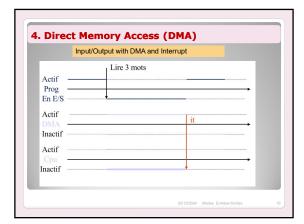

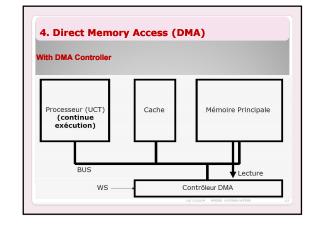

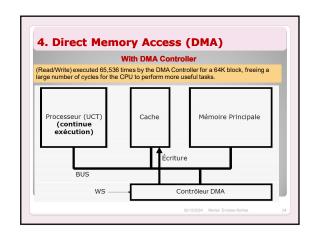

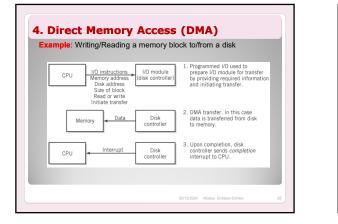

#### Operation

- > DMA takes full responsibility for transferring a block of data.

- > The CPU initiates the transfer by providing:

- 1. The identification of the concerned device,

- 2. The direction of the transfer,

- The memory address of the first word to be transferred, and the number of words involved in the transfer.

- When the transfer is complete, DMA signals to the CPU that the operation is finished via an interrupt.

## **DMA Channel Architecture**

DMA Controller: Supervises and coordinates data transfers between peripherals and memory without constant intervention from the processor. Configuration Registers: Specific registers programmed by the processor to configure transfer parameters. These registers may include the source address, destination address, amount of data to transfer, etc.

Status Registers: Used to track the current state of the transfer, such as the number of remaining data to transfer, completion status, etc.

Data Bus: The channel uses a data bus to perform the actual transfer of data between memory and peripherals.

Address Bus: Used to specify the source and destination addresses of the data during the transfer. These addresses are often stored in the configuration registers.

Control Logic: Manages the flow of operations. It decides when to initiate a transfer, when to update the status registers, and how to handle interrupts once the transfer is completed.

# Selector Channel and Multiplexer Channel Selector Channel Controls multiple high-speed I/O modules at all times. It is dedicated to transferring data from a single peripheral to memory. Multiplexer Channel Controls multiple I/O modules simultaneously. It allocates bandwidth between each device (typically lowspeed) to fetch data in turn.

5